Asia-Pacific Region Intelligence Center

삼성·SK, 차세대 HBM4 경쟁력 승부처 '1c D램' 주목 본문

삼성·SK, 차세대 HBM4 경쟁력 승부처 '1c D램' 주목

CIA bear 허관(許灌) 2024. 5. 18. 23:39

이르면 내년부터 양산이 시작되는 HBM4(6세대 고대역폭메모리)에 대한 기술 경쟁이 뜨겁다. 삼성전자가 최근 HBM4에 탑재될 D램을 한 세대 진화된 제품으로 변경하는 방안을 검토 중인 가운데, SK하이닉스도 시황에 따라 유동적인 전략을 펼칠 것으로 관측된다.

17일 업계에 따르면 삼성전자는 HBM4에 1c D램을 적용하는 방안을 검토하고 있다.

HBM은 여러 개의 D램을 수직으로 적층해 TSV(실리콘관통전극)로 연결한 메모리다. 때문에 D램 완제품의 성능이 HBM의 성능에 직접적인 영향을 끼친다.

당초 삼성전자는 내년부터 양산화되는 HBM4에 10나노급 5세대 D램인 1b D램을 적용하려고 했었다. 1b D램은 선폭이 12나노 수준으로, 삼성전자가 지난해 5월 첫 양산에 나선 제품이다. 삼성전자가 올해 양산에 나서는 HBM3E(5세대 고대역폭메모리)의 경우 1a D램이 적용됐다.

그러나 삼성전자는 최근 내부적으로 HBM4에 탑재될 D램을 1c D램으로 변경하는 방안을 수립했다. SK하이닉스, 마이크론 등 주요 경쟁사가 HBM3E에 1b D램을 적용했던 만큼, HBM4는 전공정 영역에서부터 앞서 나가겠다는 전략으로 풀이된다.

사안에 정통한 관계자는 "현재 HBM4는 12단, 16단 적층에 관계없이 1c D램으로 가는 방향"이라며 "한 세대 뒤쳐진 D램으로 전력사용량 문제가 발생한다는 우려가 많아 개발에 속도를 더하고 싶은 것으로 안다"고 밝혔다.

다만 삼성전자가 실제로 해당 방안을 실현할 지에 대해서는 아직 지켜봐야 한다는 관측도 나온다.

삼성전자가 1c D램의 초도 양산라인을 구축하는 시점은 올해 연말로, 생산능력은 월 3천장 수준으로 추산된다. 목표로 한 HBM4 양산 시점과 차이가 크지 않다.

통상 메모리 업계는 최선단 D램을 컴퓨팅·모바일용으로 순차적으로 개발하고, 이후 안정성을 확보한 뒤에 HBM에 적용하는 과정을 거쳐 왔다. 이를 고려하면 HBM4 양산 시점에 1c D램에 대한 수율을 담보하기 어려울 수 있다.

또 다른 관계자는 "삼성전자 임원진 및 실무단에서 HBM4에 1c D램을 적용하고, 양산 목표 시점 역시 내년 말에서 내년 중후반으로 앞당기는 등의 논의가 오가고 있다"며 "다만 수율이 받쳐줘야 하기 때문에 확정된 사안이 아닌, 계획 단계로 봐야한다"고 밝혔다.

한편 SK하이닉스는 삼성전자의 초기 전략과 마찬가지로 HBM4에는 1b D램을, HBM4E부터는 1c D램을 적용하는 계획을 세운 바 있다. 다만 SK하이닉스도 시황에 따라 적용 기술을 유동적으로 변경할 여지를 여전히 남겨두고 있는 것으로 알려졌다.

업계 관계자는 "삼성전자 HBM4에 적용되는 D램을 앞당기는 경우, 현재 업계 선두인 SK하이닉스 입장에서도 위기의식을 느낄 수 밖에 없다"며 "SK하이닉스도 로드맵은 세워 둔 상황이나 내부적으로 변경에 대한 여지를 계속 남겨두고 있는 것으로 안다"고 밝혔다.

삼성·SK, 차세대 HBM4 경쟁력 승부처 '1c D램' 주목 - ZDNet korea

삼성·SK, 차세대 HBM4 경쟁력 승부처 '1c D램' 주목

이르면 내년부터 양산이 시작되는 HBM4(6세대 고대역폭메모리)에 대한 기술 경쟁이 뜨겁다. 삼성전자가 최근 HBM4에 탑재될 D램을 한 세대 진화된 제품으로 변경하는 방안을 검토 중인 가운데, SK하

zdnet.co.kr

[단독] 'HBM4에 6세대 D램 탑재'…삼성전자, 승부수 띄웠다

삼성전자가 6세대 HBM(고대역폭 메모리) 코어로 한 세대 건너 뛴 1c D램을 탑재한다. 7세대 제품인 HBM4E부터 1c D램을 탑재하는 SK하이닉스보다 빠르다. 시장에서는 HBM 시장 1위 SK하이닉스를 추격하기 위한 삼성의 승부수가 던져진 것으로 보고 있다.

16일 반도체 업계에 따르면 삼성전자는 10나노급 6세대(1c) D램을 HBM4 코어 다이로 탑재한다. 삼성전자는 직전 세대 제품인 HBM3E에는 4세대(1a) D램을 사용했다. 한 세대를 건너 뛰는 것이다.

일반적으로 HBM에 들어가는 D램은 세대 순서대로 탑재된다. SK하이닉스도 HBM3E와 HBM4에는 1b를 사용했고, HBM4E부터 1c를 탑재한다.

삼성전자의 이례적인 1c D램 탑재는 적층 경쟁에서 우위를 다지기 위한 차원으로 해석된다. D램은 세대 순으로 같은 면적에 더 많은 용량을 저장할 수 있다. 예를 들어 같은 3GB를 구현하더라도 신형이 구형보다 작다. HBM에 D램을 더 높이 쌓기 위해서는 작은 칩이 유리하다. 같은 크기의 HBM이지만 전체 용량은 크게 늘릴 수 있는 셈이다.

현재 최선단 D램인 1c는 11~12nm(나노미터, 10억분의 1m) 이하 제품이다. 1a는 14나노, 1b는 12~13나노급으로 구분되고 있다.

이종환 상명대학교 시스템반도체학과 교수는 “HBM에 탑재되는 D램이 작아질수록 소비 전력도 줄어든다”면서 “더 작은 D램이 탑재되는 건 (효율 차원에서도)당연하다”고 설명했다.

문제는 개발 기간이다. 한 세대를 건너 뛴 만큼 로드맵에 맞춰 양산할 수 있는 지 여부는 여전히 미지수다. SK하이닉스가 HBM4 양산을 2025년으로 1년 앞당길 수 있었던 이유 중 하나도 HBM3E와 HBM4가 코어 다이로 같은 1b D램을 사용하기 때문으로 분석된다. 삼성전자도 내년 중 HBM4를 양산한다.

이에 대해 반도체 업계 관계자는 “안정성을 위해 1b를 탑재하는 방안도 함께 검토하고 있는 걸로 알고 있다”고 말했다.

한편 최근 삼성전자의 맹추격으로 양사간 기술격차가 상당히 압축된 것으로 평가된다. 지난달 월스트리트저널(WSJ)은 “삼성전자가 상반기 차세대 HBM을 양산하면, 이전 세대 HBM 칩처럼 1년이 아닌 분기(3개월) 정도만 뒤 처지게 되는 의미를 갖는다”고 분석한 바 있다.

http://m.viva100.com/view.php?key=20240516010004889

[단독] `HBM4에 6세대 D램 탑재`…삼성전자, 승부수 띄웠다

삼성전자가 6세대 HBM(고대역폭 메모리) 코어로 한 세대 건너 뛴 1c D램을 탑재한다. 7세대 제품인 HBM4E부터 1c D램을 탑재하는 SK하이닉스보다 빠르다. 시장에서는 H..

www.viva100.com

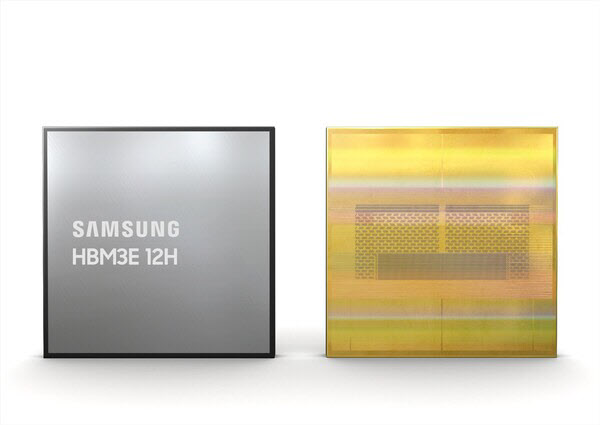

삼성전자, 업계 최초 36GB HBM3E 12H D램 개발

삼성전자가 업계 최초로 36GB(기가바이트) HBM3E(5세대 HBM) 12H(High, 12단 적층) D램 개발에 성공하고 고용량 HBM 시장 선점에 나선다.

삼성전자는 24Gb(기가비트) D램 칩을 TSV(Through-Silicon Via, 실리콘 관통 전극) 기술로 12단까지 적층해 업계 최대 용량인 36GB HBM3E 12H를 구현했다.

* 24Gb(기가비트) D램 용량 = 3GB(기가바이트)

* HBM3E 12H D램 용량 : 36GB (3GB D램 x 12)

* TSV: 수천 개의 미세 구멍을 뚫은 D램 칩을 수직으로 쌓아 적층된 칩 사이를 전극으로 연결하는 기술

HBM3E 12H는 초당 최대 1,280GB의 대역폭과 현존 최대 용량인 36GB을 제공해 성능과 용량 모두 전작인 HBM3(4세대 HBM) 8H(8단 적층) 대비 50% 이상 개선된 제품이다.

* HBM3E 12H는 1,024개의 입출력 통로(I/O)에서 초당 최대 10Gb를 속도를 지원함. 초당 1,280GB를

처리할 수 있어 1초에 30GB 용량의 UHD 영화 40여편을 업(다운)로드 할 수 있는 속도

* 성능은 고객사 모의 환경 기반의 내부 평가 결과이며, 실제 환경에 따라 변동 가능

삼성전자는 'Advanced TC NCF'(Thermal Compression Non Conductive Film, 열압착 비전도성 접착 필름) 기술로 12H 제품을 8H 제품과 동일한 높이로 구현해 HBM 패키지 규격을 만족시켰다.

'Advanced TC NCF' 기술을 적용하면 HBM 적층수가 증가하고, 칩 두께가 얇아지면서 발생할 수 있는 '휘어짐 현상'을 최소화 할 수 있는 장점이 있어 고단 적층 확장에 유리하다.

삼성전자는 NCF 소재 두께도 지속적으로 낮춤으로써, 업계 최소 칩간 간격인 '7마이크로미터(um)'를 구현했다. 이를 통해 HBM3 8H 대비 20% 이상 향상된 수직 집적도를 실현했다.

특히, 칩과 칩사이를 접합하는 공정에서 신호 특성이 필요한 곳은 작은 범프를, 열 방출 특성이 필요한 곳에는 큰 범프를 목적에 맞게 사이즈를 맞춰 적용했다. 크기가 다른 범프 적용을 통해 열 특성을 강화하는 동시에 수율도 극대화했다.

* 범프(Bump): 칩 사이를 전기적으로 연결하기 위해 형성한 전도성 돌기를 통칭

또한, 삼성전자는 NCF로 코팅하고 칩을 접합해 범프 사이즈를 다양하게 하면서 동시에 공극(Void)없이 적층하는 업계 최고 수준의 기술력도 선보였다.

삼성전자가 개발에 성공한 HBM3E 12H는 AI 서비스의 고도화로 데이터 처리량이 급증하는 상황 속에서 AI 플랫폼을 활용하는 다양한 기업들에게 최고의 솔루션이 될 것으로 기대된다.

특히, 성능과 용량이 증가한 이번 제품을 사용할 경우 GPU 사용량이 줄어 기업들이 총 소유 비용(TCO, Total Cost of Ownership)을 절감할 수 있는 등 리소스 관리를 유연하게 할 수 있는 것도 큰 장점이다.

예를 들어 서버 시스템에 HBM3E 12H를 적용하면 HBM3 8H를 탑재할 때 보다 평균 34% AI 학습 훈련 속도 향상이 가능하며, 추론의 경우에는 최대 11.5배 많은 AI 사용자 서비스가 가능할 것으로 기대된다.

* 동일 GPU 인프라 조건에서 내부 데이터와 시뮬레이션을 기반으로 산출한 값

삼성전자 메모리사업부 상품기획실장 배용철 부사장은 "삼성전자는 AI 서비스를 제공하는 고객사의 고용량 솔루션 니즈에 부합하는 혁신 제품 개발에 힘쓰고 있다"며 "앞으로 HBM 고단 적층을 위한 기술 개발에 주력하는 등 고용량 HBM 시장을 선도하고 개척해 나갈 것"이라고 밝혔다.

한편, 삼성전자는 HBM3E 12H의 샘플을 고객사에게 제공하기 시작했으며 상반기 양산할 예정이다.

삼성전자, 업계 최초 36GB HBM3E 12H D램 개발 | 삼성반도체 (samsung.com)

삼성전자, 업계 최초 36GB HBM3E 12H D램 개발 | 삼성반도체

삼성전자가 업계 최초로 36GB(기가바이트) HBM3E(5세대 HBM) 12H(High, 12단 적층) D램 개발에 성공하고 고용량 HBM 시장 선점에 나선다.

semiconductor.samsung.com

- HBM3E 12H(12단 적층)개발 … 업계 최대 용량 36GB 구현

- 기존 HBM3 8H(8단 적층)대비 성능과 용량 모두 50% 이상 향상

- 'Advanced TC NCF' 기술 활용해 8단과 동일한 높이로 12단 적층 구현

- 업계 최소 7마이크로미터 칩간 간격 … 수직 집적도 개선

- 다양한 사이즈의 범프 적용을 통한 열특성 강화 효과

- 고객사 샘플 제공 시작, 상반기 양산 예정

'Guide Ear&Bird's Eye6 > 산업의 쌀 반도체(5G. 인공지능, 자율주행. 태양광 재생에너지 등 )' 카테고리의 다른 글

| 삼성, 2나노 AP '테티스' 프로젝트 착수...2026년 '갤럭시 S26' 탑재 예상 (0) | 2024.05.23 |

|---|---|

| 엔비디아 '시장전망 상회' 호실적 지속…"AI 열풍 계속 확인" (0) | 2024.05.23 |

| 삼성전자, 5대 매출처에 퀄컴 빠지고...中 반도체 유통망 2곳 포함 (0) | 2024.05.18 |

| 최상목 “10조 이상 규모의 반도체 지원 프로그램 신설” (0) | 2024.05.12 |

| 인텔과 일본 기업 14개사, 반도체 후공정 자동화 공동개발 (0) | 2024.05.08 |