Asia-Pacific Region Intelligence Center

[인터뷰] AI 시대 삼성전자 HBM이 만들어 내는 완벽한 하모니 본문

[인터뷰] AI 시대 삼성전자 HBM이 만들어 내는 완벽한 하모니

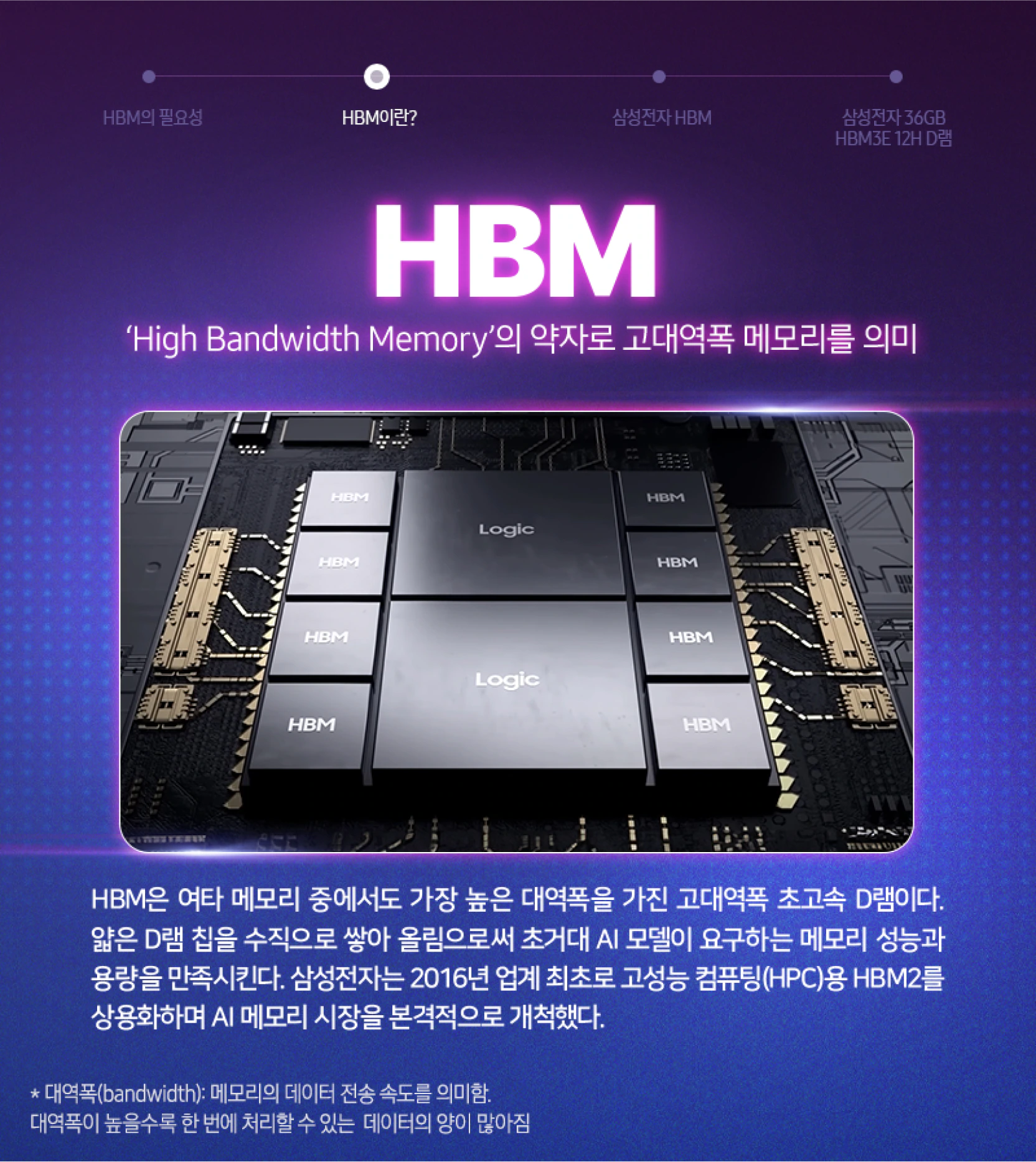

CIA Bear 허관(許灌) 2024. 5. 24. 09:45고대역폭 메모리 'HBM(High Bandwidth Memory)'은 초거대 AI 시대라는 악곡(樂曲)의 뛰어난 오케스트라 연주자로 비유할 수 있다. 마치 능숙한 연주자가 빠르고 정확하게 멜로디를 연주하는 것처럼, HBM은 높은 대역폭을 기반으로 AI의 방대한 데이터를 효율적으로 처리한다.

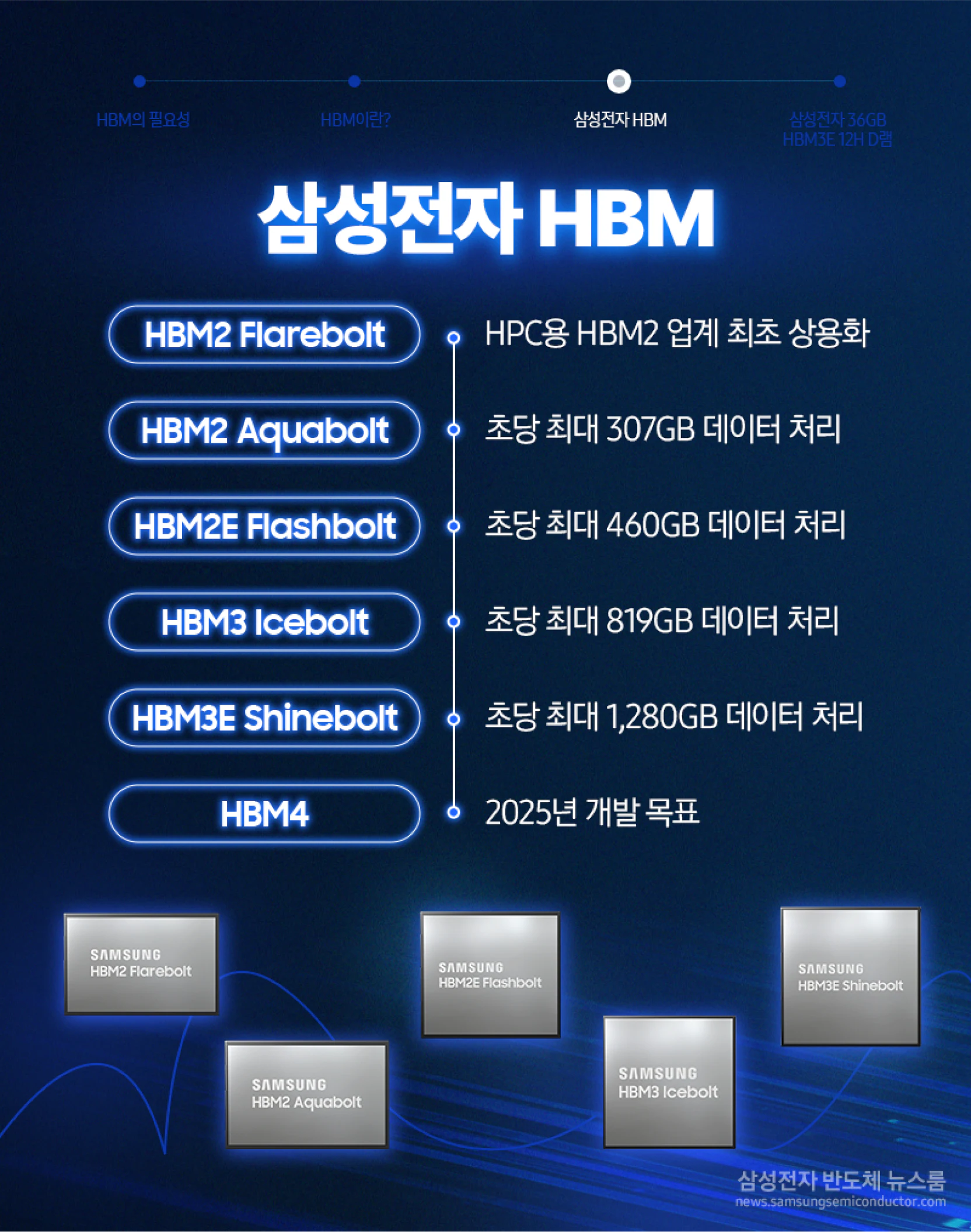

삼성전자는 2024년 2월, 업계 최초로 36GB HBM3E(5세대 HBM) 12H D램 개발에 성공했다. 36GB HBM3E 12H D램은 24Gb D램 칩을 TSV(Through-silicon Via, 실리콘 관통 전극) 기술로 12단까지 적층한 메모리다. 해당 제품은 지난달 엔비디아의 연례 개발자 콘퍼런스 'GTC(GPU Technology Conference) 2024'에서 공개되어 고객들로부터 뜨거운 반응을 받기도 했다.

이에 뉴스룸은 삼성전자 HBM을 담당하는 상품기획실 김경륜 상무와 DRAM개발실 윤재윤 상무를 만나 보았다. 두 담당자의 인터뷰를 통해 기술 혁신을 이끄는 삼성전자의 HBM을 들여다보자.

삼성전자는 2016년 업계 최초로 AI 메모리 시장의 막을 연 이래 독보적인 기술 노하우를 바탕으로 AI 반도체 생태계를 확장해 왔다. 초격차 기술력으로 무한한 가능성을 열어 온 삼성전자가 그려 갈 앞으로의 미래가 기대된다.

[인터뷰] AI 시대 삼성전자 HBM이 만들어 내는 완벽한 하모니 | 삼성반도체 (samsung.com)

[인터뷰] AI 시대 삼성전자 HBM이 만들어 내는 완벽한 하모니 | 삼성반도체

삼성전자는 2024년 2월, 업계 최초로 36GB HBM3E(5세대 HBM) 12H D램 개발에 성공했다.

semiconductor.samsung.com

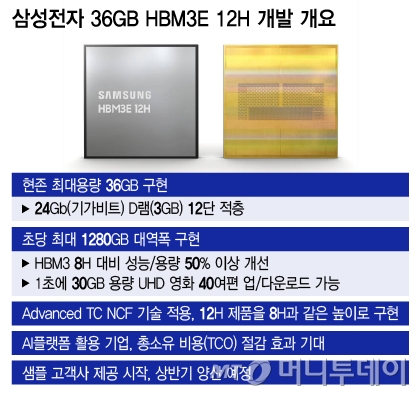

삼성전자, 업계 최초 36GB HBM3E 12H D램 개발

- HBM3E 12H(12단 적층)개발 … 업계 최대 용량 36GB 구현

- 기존 HBM3 8H(8단 적층)대비 성능과 용량 모두 50% 이상 향상

- 'Advanced TC NCF' 기술 활용해 8단과 동일한 높이로 12단 적층 구현

- 업계 최소 7마이크로미터 칩간 간격 … 수직 집적도 개선

- 다양한 사이즈의 범프 적용을 통한 열특성 강화 효과

- 고객사 샘플 제공 시작, 상반기 양산 예정

삼성전자가 업계 최초로 36GB(기가바이트) HBM3E(5세대 HBM) 12H(High, 12단 적층) D램 개발에 성공하고 고용

량 HBM 시장 선점에 나선다.

삼성전자는 24Gb(기가비트) D램 칩을 TSV(Through-Silicon Via, 실리콘 관통 전극) 기술로 12단까지 적층해 업계 최대 용량인 36GB HBM3E 12H를 구현했다.

* 24Gb(기가비트) D램 용량 = 3GB(기가바이트)

* HBM3E 12H D램 용량 : 36GB (3GB D램 x 12)

* TSV: 수천 개의 미세 구멍을 뚫은 D램 칩을 수직으로 쌓아 적층된 칩 사이를 전극으로 연결하는 기술

HBM3E 12H는 초당 최대 1,280GB의 대역폭과 현존 최대 용량인 36GB을 제공해 성능과 용량 모두 전작인 HBM3(4세대 HBM) 8H(8단 적층) 대비 50% 이상 개선된 제품이다.

* HBM3E 12H는 1,024개의 입출력 통로(I/O)에서 초당 최대 10Gb를 속도를 지원함. 초당 1,280GB를

처리할 수 있어 1초에 30GB 용량의 UHD 영화 40여편을 업(다운)로드 할 수 있는 속도

* 성능은 고객사 모의 환경 기반의 내부 평가 결과이며, 실제 환경에 따라 변동 가능

삼성전자는 'Advanced TC NCF'(Thermal Compression Non Conductive Film, 열압착 비전도성 접착 필름) 기술로 12H 제품을 8H 제품과 동일한 높이로 구현해 HBM 패키지 규격을 만족시켰다.

'Advanced TC NCF' 기술을 적용하면 HBM 적층수가 증가하고, 칩 두께가 얇아지면서 발생할 수 있는 '휘어짐 현상'을 최소화 할 수 있는 장점이 있어 고단 적층 확장에 유리하다.

삼성전자는 NCF 소재 두께도 지속적으로 낮춤으로써, 업계 최소 칩간 간격인 '7마이크로미터(um)'를 구현했다. 이를 통해 HBM3 8H 대비 20% 이상 향상된 수직 집적도를 실현했다.

특히, 칩과 칩사이를 접합하는 공정에서 신호 특성이 필요한 곳은 작은 범프를, 열 방출 특성이 필요한 곳에는 큰 범프를 목적에 맞게 사이즈를 맞춰 적용했다. 크기가 다른 범프 적용을 통해 열 특성을 강화하는 동시에 수율도 극대화했다.

* 범프(Bump): 칩 사이를 전기적으로 연결하기 위해 형성한 전도성 돌기를 통칭

또한, 삼성전자는 NCF로 코팅하고 칩을 접합해 범프 사이즈를 다양하게 하면서 동시에 공극(Void)없이 적층하는 업계 최고 수준의 기술력도 선보였다.

삼성전자가 개발에 성공한 HBM3E 12H는 AI 서비스의 고도화로 데이터 처리량이 급증하는 상황 속에서 AI 플랫폼을 활용하는 다양한 기업들에게 최고의 솔루션이 될 것으로 기대된다.

특히, 성능과 용량이 증가한 이번 제품을 사용할 경우 GPU 사용량이 줄어 기업들이 총 소유 비용(TCO, Total Cost of Ownership)을 절감할 수 있는 등 리소스 관리를 유연하게 할 수 있는 것도 큰 장점이다.

예를 들어 서버 시스템에 HBM3E 12H를 적용하면 HBM3 8H를 탑재할 때 보다 평균 34% AI 학습 훈련 속도 향상이 가능하며, 추론의 경우에는 최대 11.5배 많은 AI 사용자 서비스가 가능할 것으로 기대된다.

* 동일 GPU 인프라 조건에서 내부 데이터와 시뮬레이션을 기반으로 산출한 값

삼성전자 메모리사업부 상품기획실장 배용철 부사장은 "삼성전자는 AI 서비스를 제공하는 고객사의 고용량 솔루션 니즈에 부합하는 혁신 제품 개발에 힘쓰고 있다"며 "앞으로 HBM 고단 적층을 위한 기술 개발에 주력하는 등 고용량 HBM 시장을 선도하고 개척해 나갈 것"이라고 밝혔다.

한편, 삼성전자는 HBM3E 12H의 샘플을 고객사에게 제공하기 시작했으며 상반기 양산할 예정이다.

삼성전자, 업계 최초 36GB HBM3E 12H D램 개발 | 삼성반도체

삼성전자가 업계 최초로 36GB(기가바이트) HBM3E(5세대 HBM) 12H(High, 12단 적층) D램 개발에 성공하고 고용량 HBM 시장 선점에 나선다.

semiconductor.samsung.com

- SK하이닉스가 HBM 시장에서 두각을 나타내고 있는 원동력은 바로 MR-MUF란 기술 때문이다. MR-MUF는 일종의 패키징에 들어가는 하나의 공정 기술이다. MR-MUF는 반도체 칩을 회로에 부착하고 칩을 위로 쌓아 올릴 때 칩과 칩 사이 공간을 EMC라는 물질로 채워주고 붙여주는 공정을 말한다.

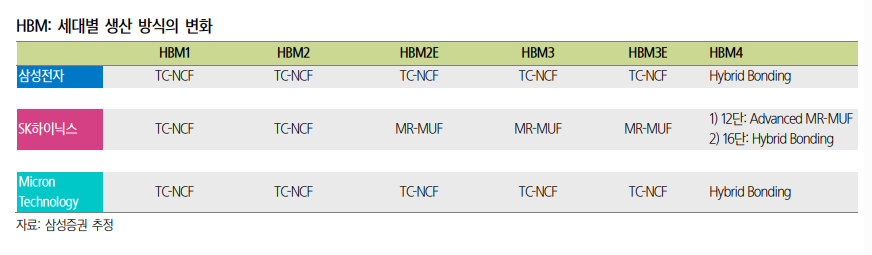

지금까지는 이 공정에 NCF 기술을 활용했다. NCF는 칩을 쌓아 올릴 때 칩과 칩 사이에 일종의 필름을 사용해서 쌓는 방식이다. 삼성전자와 SK하이닉스, 마이크론 등 D램 업체들은 NCF 기술을 적용했다. SK하이닉스는 3세대 HBM인 HBM2E부터 이 방식을 적용하고 있다.

당초 삼성전자 등 경쟁 업체들은 MR-MUF를 적용하는 것은 불가능할 것이라 내다봤다. 하지만 SK하이닉스 PKG개발 조직이 일본 나믹스(NAMICS)란 기업을 통해 소재를 공급받아 개발에 성공했다. 이 같은 소식에 삼성전자 등 주요 D램 업체들은 적잖이 놀란 것으로 전해진다. 삼성전자 역시 현재 MR-MUF 방식을 연구 중인 것으로 전해진다.

업계 한 관계자는 “MR-MUF 방식은 NCF 대비 열전도율이 2배 가량 높고 공정 속도는 물론 수율 등에도 영향을 준다”며 “지금은 비록 초기 단계지만 내년부터 HBM3 시장이 본격적으로 확대될 것”이라고 말했다.

- AI 칩 시장의 폭발적인 성장에 따라 삼성전자와 SK하이닉스의 고대역폭메모리(HBM) 칩 시장 기대감이 지속적으로 커지는 가운데, 관련 메모리 칩의 핵심 기술을 구현하기 위해서는 국내 기업들이 반드시 일본 소재 기업들과 협력해야 하는 것으로 나타났다.

반도체 기업 최초 시가총액 1조달러(약 1300조원) 시대를 연 엔비디아의 AI용 첨단 그래픽처리장치(GPU) 수요가 급격히 증가하면서, 한국 기업을 등에 업은 일본 기업들이 뒤에서 ‘조용한 수혜’를 누리고 있다는 분석이다.

6일 업계에 따르면 삼성전자와 SK하이닉스는 HBM3 관련 핵심 기술을 구현하는 과정에서, 각각 일본의 ‘레조낙’과 ‘나믹스’라는 회사에서 주요 소재를 공급받고 있다. HBM3는 HBM 제품 중 4세대에 해당하는 것으로, 현재 엔비디아의 최첨단 GPU인 ‘H100’에 탑재되며 요즘 가장 각광받고 있는 메모리 칩으로 분류된다.

이 HBM은 D램 칩들을 수직으로 쌓고 실리콘관통전극(TSV) 공법을 통해 연결해 만든다. 그런데 이렇게 위와 아래로 쌓인 칩들을 TSV 공법으로 연결하기 위해서는 울퉁불퉁하게 튀어나온 범프(반도체 칩과 기판을 연결하는 구 형태의 돌기)를 활용하게 되는데, 이 때 중요한 것이 범프 간의 공간을 메우는 작업이다.

삼성전자는 일본 레조낙에서 받아온 ‘논컨덕티드필름(NCF)’을 넣어 빈틈을 메꾼다. 칩 사이에 NCF라는 절연 필름(에폭시와 아크릴이 혼재)을 덧대고, 여기에 열과 압력을 가해 위 쪽을 꾹 눌러서 붙여 절연 필름이 녹아 접착되도록 한다.지난 7월 진행된 2분기 컨퍼런스콜에서 삼성전자는 이 기술의 강점을 특별히 강조하기도 했다. 삼성전자 관계자는 “훨씬 더 개선된 최첨단 NCF 소재를 새롭게 개발해 현재 양산 중인 HBM3 제품에 적용하고 있으며, 향산된 품질과 양산성을 확보하여 고객에 출하 중”이라고 전했다.

삼성전자와 달리 SK하이닉스는 필름을 사용하지 않는다. ‘매스 리플로우 몰디드 언더필(MR-MUF)’ 방식을 통해 HBM3를 만들고 있다. MR-MUF는 SK하이닉스가 최초로 개발한 기술로 현재도 SK하이닉스만 이 기술을 사용해 HBM을 만드는 것으로 알려졌다. 회사는 현재 양산 중인 HBM3을 넘어 내년에 출시 예정인 제품(HBM3E)에서도 시장 경쟁력을 유지하는 데 MR-MUF 방식이 주효할 것으로 관측하고 있다.

MR-MUF 패키지는 반도체 칩을 회로에 부착하고 칩을 위로 쌓아 올릴 때 칩과 칩 사이 공간을 ‘에폭시몰딩컴파운드(EMC)’라는 물질로 채워주고 붙여주는 공정을 말한다. EMC는 칩과 칩 사이 회로를 보호하기 위해 주입된 ‘액체 형태 보호재’이다.

이 액체 형태의 보호재는 일본의 나믹스라는 기업에서 공급된다. 업계에 따르면 EMC를 생산하는 기업들은 많지만, SK하이닉스의 HBM3를 생산하는 데 사용되는 물질은 나믹스에서만 유일하게 공급하고 있는 상태다.

현재 엔비디아가 양산하며 없어서 못팔 정도라는 첨단 GPU인 ‘H100’에 SK하이닉스의 MR-MUF 방식이 적용된 HBM3가 탑재되고 있다. 삼성전자는 아직 정식 양산 계약을 체결하진 않았으나, NCF를 통해 만든 HBM3와 관련해, 연내 엔비디아 공급 가능성이 유력하게 대두되고 있다. 삼성전자까지 엔비디아 공급이 최종 확정되면, 삼성과 SK하이닉스 모두 관련 수혜를 누리게 될 전망이다. 동시에 이들 기업에 핵심 소재를 제공하는 일본 기업들의 입지 역시 한층 부각될 것이란 분석이다.

이에 따라 삼성전자와 SK하이닉스 역시 일본 소재 기업과의 협력 다각화를 위한 다양한 논의를 하고 있다는 후문이다. 업계 관계자는 “현재 일본 소재 기업들이 다양한 글로벌 메모리 업체들로부터 HBM 관련 소재 공급을 위한 논의를 진행 중”이라고 말했다.

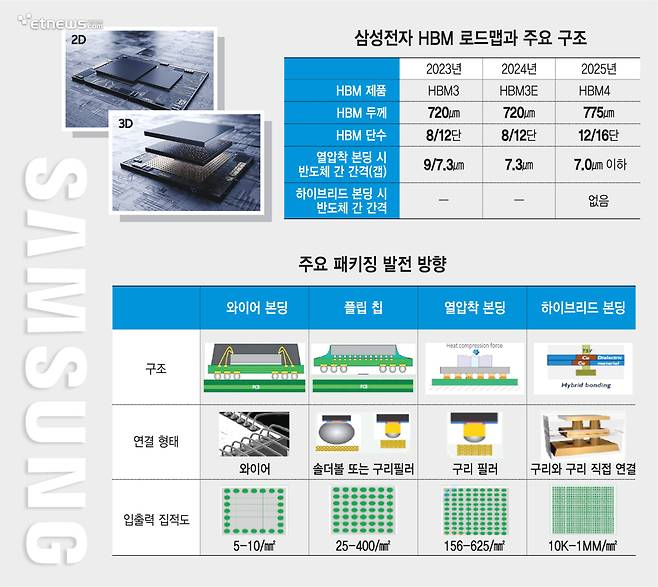

- 고대역폭메모리(HBM)는 D램을 여러 개 쌓아 연결한 고성능 반도체다. 처음 4단으로 쌓았던 HBM은 8단에 이어 현재 12단까지 나왔고, 현재 16단이 개발 중이다. 와이어(금속 전선) 없이 다수의 D램을 수직 관통하는 전극으로 연결하기 때문에, 칩을 잘 연결하고 보호할 수 있는 기술이 중요하다. 이 HBM 개발 경쟁은 국내 반도체 기업인 SK하이닉스와 삼성전자가 주도하고 있는데, 두 회사의 패키징 공법은 차이가 있다. SK 하이닉스는 ‘MR-MUF(Mass Reflow-Molded UnderFill)’, 삼성전자는 ‘TC NCF(Thermal Compression Non Conductive Film)’ 기술을 적용하고 있다. 쉽게 말하면 SK하이닉스는 오븐에서 한 번에 구워내는 방식, 삼성전자는 필름을 한 장씩 깔아가면서 쌓는 방식이다

SK하이닉스의 MR-MUF는 여러 층의 D램을 한 번에 포장하는 기술이다. D램 아래에는 칩을 연결할 수 있는 납 소재의 ‘범프’가 있다. 열을 가해 모든 범프를 한 번에 녹여 납땜하는 기술이 MR이다. 이를 통해 D램을 모두 연결한 뒤 칩을 보호하는 작업이 이뤄진다. 이것이 MUF다. 방열 효과가 뛰어난 에폭시 밀봉재(보호재)를 주입해 칩 사이를 채우고 칩과 그 주변을 감싸게 된다. 이후 열과 압력을 가해 굳히면 HBM이 완성된다. SK하이닉스는 “오븐에 굽듯 열을 고르게 가하고 모든 칩을 한 번에 접착하기에 안정적이고 효율적이다”라고 설명한다.

삼성전자의 TC NCF 방식은 조금 다르다. ‘열압착 비전도성 접착 필름’이라고 불리는 방식이다. 칩을 한 층씩 쌓아 연결할 때마다 그 사이에 비전도성 접착 필름을 넣는다. 필름은 칩 사이를 절연시키고 충격으로부터 연결 부위를 보호하기 위해 사용하는 고분자 물질이다. 삼성전자는 NCF 소재 두께를 점차 줄여나가 5세대인 HBM3E 12단에는 7마이크로미터(㎛)까지 줄였다. 삼성전자는 “층수가 늘어나고 칩 두께가 얇아지면서 발생할 수 있는 ‘휘어짐 현상’을 최소화할 수 있는 장점이 있어 높이 쌓는 데 유리하다”고 했다.

SK하이닉스는 MR-MUF의 안정적인 특성을 바탕으로 4세대인 HBM3 시장에서 앞서 나가고 있다. SK하이닉스의 HBM3는 엔비디아에 사실상 독점 공급되고 있다. 반면 삼성전자는 TC NCF 가 높은 단을 쌓을 때 더 유리하다는 장점을 내세워 차세대 HBM 경쟁에서 우위를 차지하겠다는 전략이다.

HBM(고대역폭메모리) 시장 주도권을 쥐기 위한 '패키징 기술 경쟁'이 격화하고 있다. SK하이닉스가 독자 개발한 패키징 기술을 기반으로 4세대 HBM 시장을 선도하는 가운데 삼성전자는 SK하이닉스와 다른 패키징 공정을 고도화해 5세대 시장에 뛰어들었다. 6세대 HBM 시장에선 누가 먼저 칩과 칩을 바로 붙이는 '하이브리드 본딩' 공정 적용에 성공하느냐를 두고 치열한 경쟁이 벌어질 전망이다.

4일 업계에 따르면 삼성전자는 최근 개발한 12단 HBM3E(5세대)에 '어드밴스드(Advanced) TC-NCF' 공정을 적용했다.

TC-NCF는 반도체 칩 사이에 NCF라는 필름을 덧대고 열과 압력을 가해 칩을 결합하는 공정이다. 삼성전자는 어드밴스드 기술을 적용해 얇은 반도체 칩을 많이 쌓을 때 발생하는 '휘어짐'을 최소화했다. 종전보다 얇은 필름(NCF)을 사용해 칩 사이 간격을 줄였고, 크기가 다른 범프(칩을 전기적으로 연결하는 돌기)를 적용해 열 방출 성능과 수율을 높였다.

업계는 삼성전자의 어드밴스드 TC-NCF 기술 개발을 의미 있게 평가했다. 기존 TC-NCF는 SK하이닉스가 적용한 MR-MUF 공정 대비 낮은 열 방출 성능 및 수율 등 단점이 지적됐는데 이를 삼성전자가 보완한 것이기 때문이다.

MR-MUF는 반도체 칩 사이 회로를 보호하기 위해 액체 형태의 보호재를 주입해 굳히는 공정이다. SK하이닉스도 과거에는 TC-NCF를 적용했지만 HBM2E(3세대)부터 독자 개발한 MR-MUF 공정을 채택했다. HBM3(4세대) 생산에는 어드밴스드 MR-MUF 기술을 적용해 공정 효율과 제품 성능 안정성을 높였다. SK하이닉스가 HBM 시장 1위를 유지하는 비결 중 하나로 MR-MUF 공정 도입이 꼽힌다.

일각에선 향후 삼성전자도 SK하이닉스처럼 MR-MUF 공정으로 전환할 것이란 전망이 나온다. 다만 삼성전자가 이번 어드밴스드 TC-NCF 기술 개발에 성공했고, 그동안 대규모 투자로 구축한 TC-NCF 라인을 전면 전환하는 것이 쉽지 않은 점 등을 고려할 때 TC-NCF를 고수할 것이란 관측도 동시에 나온다. 최근 HBM3E(5세대) 양산을 시작한 미국 마이크론도 TC-NCF를 적용한 것으로 알려졌다.

HBM4(6세대)부터는 하이브리드 본딩 적용 경쟁이 본격화할 것으로 보인다. 하이브리드 본딩은 범프 없이 구리로 반도체 칩을 직접 연결하는 방식이다. 제품 두께는 줄이고 신호 전송 속도를 높일 수 있는 게 특징이다.

황상준 삼성전자 메모리사업부 D램 개발실장(부사장)은 지난해 10월 "HBM4 제품에 적용하기 위한 고온 열특성에 최적화된 NCF 조립 기술과 하이브리드 본딩 기술도 준비 중"이라고 밝혔다. 문기일 SK하이닉스 부사장도 지난해 8월 "12단 적층 HBM의 다음 제품인 고용량, 고적층 HBM에 하이브리드 본딩을 적용할 계획으로 기술을 개발하고 있다"고 했다.

반도체 업계 관계자는 "TC-NCF와 MR-MUF는 각각 장단점이 있어 어떤 공정이 명확히 더 낫다고 말하기 어렵다"며 "삼성전자와 SK하이닉스 모두 궁극적으로는 하이브리드 본딩 적용을 위해 패키징 사업 역량을 모으고 있을 것"이라고 말했다.

SK하이닉스, MR-MUF 독점…삼성 'NCF' 유지

최근 삼성전자가 고대역폭메모리(HBM)4에 몰디드 언더필(MUF) 방식을 적용할 것이라는 이야기가 나오고 있지만 SK하이닉스가 핵심 소재 공급선과 독점 계약을 해 진입이 쉽지 않을 전망이다.

삼성전자도 차세대 서버용 D램 모듈에는 MUF 적용을 검토 중이지만 HBM에는 쓰기 어렵다고 판단, HBM에는 하이브리드 본딩을 선제 도입하는 방식으로 나갈 것으로 예상되고 있다. 다만 HBM4 두께가 완화되는 표준이 정해지면서 양사는 한동안 기존 방식을 고수하면서 차세대 본딩 기술 개발에 힘쓸 전망이다.

반도체 업계에 따르면 SK하이닉스는 일본 전자부품 재료업체 나믹스(NAMICS)를 통해 매스 리플로우 몰디드 언더필(MR-MUF) 소재를 독점 공급받고 있다. 삼성전자가 MUF 방식을 도입하기 위해서는 나믹스가 아닌 새로운 기업으로부터 소재를 공급 받아야 하는 상황이다.

이민희 BNK투자증권 연구원은 "HBM4부터 경쟁사의 MR-MUF 기술 도입 가능성이 있으나 SK하이닉스가 핵심 소재 공급선을 독점 계약했기 때문에 한동안 진입은 쉽지 않을 전망"이라며 "MR-MUF 기술 우수성이 입증되고 있고, 최소 HBM3E까지는 경쟁사들의 진입이 제한적인 수준일 것"이라고 말했다.

앞서 업계에서는 삼성전자가 첨단 반도체 패키징 실리콘관통전극(TSV) 공정에 MUF 소재 도입을 검토하고 있다는 소식이 나오면서 HBM에도 적용되는 것이 아니냐는 관측이 나오기도 했다. MUF 방식은 현재 HBM 시장에서 두각을 나타내고 있는 SK하이닉스가 사용하는 기술로, 기존 MR(매스 리플로우, 납땜)을 응용한 것이다. 반면 삼성전자와 마이크론은 HBM에 TC(열압착)-NCF 방식을 쓰고 있다.

MR-MUF는 반도체 칩을 회로에 부착하고 칩을 위로 쌓아 올릴 때 칩과 칩 사이 공간을 액체 물질의 에폭시몰딩컴파운드(EMC)로 채워주고 붙여주는 공정을 말한다. 반면 삼성전자는 반도체를 수직 연결할 때 독자 개발한 비전도성 접착 필름(NCF)을 사용하고 있다. NCF는 칩을 쌓아 올릴 때 칩과 칩 사이에 일종의 내구성이 강한 필름을 사용해서 쌓아 칩이 휘어지는 현상을 방지한다.

SK하이닉스는 자체 개발한 MR-MUF 기술을 통해 HBM3부터 삼성전자와 마이크론을 제치고 시장에서 독점적 지위를 가져가며 1위를 하고 있다. 이에 삼성전자도 지난해부터 MUF 소재 적용 검토를 시작했다. 다만 기존에 SK하이닉스가 사용하고 있는 소재는 일본 나믹스를 통해 독점 공급되면서 삼성전자가 사용하기가 어려운 상황이었다. 이에 삼성SDI 등을 통해 소재 공급을 검토했다.

하지만 실제 테스트 결과 HBM에서 MUF 기술을 도입하는데는 무리가 있다고 판단, 차세대 서버용 D램 모듈에 적용하는 쪽으로 선회했다. 서버D램은 적층 층수가 4단에 그치고, TSV로 형성하는 입‧출구(I/O) 개수 또한 30여개(HBM3E 1024개)에 그쳐 MUF 도입이 용이하다.

김영건 미래에셋증권 연구원은 "삼성전자가 HBM3E까지는 NCF 방식을 고수하고, 2026년 양산 예정인 HBM4에서 하이브리드 본딩에 대한 적용 가능성을 높여갈 것"이라며 "와이어본딩 대신 TSV로 연결하는 고성용 서버 D램 모델에 대한 MUF 적용 여부 검토가 와전되면서 HBM에도 MUF를 도입하는 것으로 오해를 불러일으켰다"고 전했다.

삼성전자는 TC-NCF 방식을 고수하면서 하이브리드 본딩 방식으로 넘어갈 가능성이 높다. SK하이닉스도 MR-MUF에서 진화한 어드밴스드 MR-MUF를 적용하다가 결국 하이브리드로 넘어갈 것으로 예상된다.

다만 최근 국제반도체표준화기구(제덱, JEDEC)가 HBM4의 표준을 720마이크로미터(μm) 보다 두꺼운 775마이크로미터로 패키지 두께 기준을 완화하면서 한동안은 기존 본딩 기술이 유지될 가능성이 높아졌다.

최근 D램 적층수가 늘어나면서 반도체 제조사 입장에서 HBM 패키지 두께를 유지하기가 어려워졌다. 패키지 두께를 줄이기 위해서는 하이브리드본딩 기술에 막대한 투자가 필요하고, 아직 기술적 완성도도 부족한 상황이었다. 하지만 두께 완화로 기존 본딩 기술로도 16단 D램 적층 HBM4을 충분히 구현할 수 있게 됐다.

하이브리드 본딩은 웨이퍼나 다이를 적층해 하나의 반도체를 만드는 방식으로 차세대 패키징 기술로 주목받고 있는 기술이다. 입출력(I/O)과 배선 길이 등을 개선할 수 있다는 장점이 있다.

김영건 연구원은 "하이브리드 본딩에 대한 기술적‧수익성 측면에서 한계가 지적되는 부분도 있다"면서도 "하지만 향후 HBM 뿐 아니라 파운드리나 3D 패키징 등으로의 확장성이 큰 기술"이라고 전했다.

-하이브리드 본딩 기술은 범프와 같은 매개체 없이 구리 배선의 패드끼리 직접 결합하여 칩과 칩을 포개는 기술이며 기존 flip-chip 본딩에 비해 전기신호 밀도를 1,000배 이상 높일 수 있다. 또한 이 기술로 마이크로 범프 기술로 불가능했던 10um 이하로 pitch를 줄이는 것이 가능해졌다.

하이브리드 본딩 앞세운 삼성, 첨단 패키징 시장 잡는다

삼성전자가 첨단 반도체 패키징 기술에 사활을 걸었다. 반도체 성능 한계를 극복할 3차원(3D) 적층 구조를 구현, 차세대 반도체 시장 주도권을 확보하기 위해서다. 이르면 2026년 하반기 3D 모바일 애플리케이션프로세서(AP) 양산 기술을 확보한다는 로드맵 역시 이같은 전략의 발로다.

삼성전자가 3D 적층 반도체를 개발하는데는 '하이브리드 본딩' 기술이 핵심이다. 차세대 반도체 패키징 기술로 손꼽히는 하이브리드 본딩을 앞세워 메모리 뿐 아니라 시스템 반도체 패권까지 쥐는 것이 목표다. 인공지능(AI) 반도체에 꼭 필요한 고대역폭메모리(HBM)부터 AP와 같은 시스템 반도체까지 하이브리드 본딩 적용 저변이 확대되고 있다. 이에 따라 반도체 패키징 공급망 변화가 불가피하다.

◇시스템 반도체 입출력 수 대폭 증가…신호 전달 속도↑

삼성전자는 2014년 3D 구조의 AP 기술을 확보한 바 있다. 이 때는 열압착 본딩(TCB) 방식으로, 상하 반도체(다이) 연결에 솔더볼(마이크로 범프)이 쓰였다. 이후 솔더볼은 D램 적층에도 활용, HBM까지 적용되고 있다.

상하 반도체 적층을 위해서는 우선 실리콘관통전극(TSV) 공정이 필요하다. 반도체에 미세 구멍(비아 홀)을 뚫어 그 사이에 구리 등 금속을 연결한다. 그 끝단에 솔더볼을 부착, 위·아래 반도체를 전기적으로 연결하는 방식이다.

납땜용 구슬인 솔더볼은 TSV을 연결하는 구리와 다른 저항값을 가지고 있다. 이 때문에 전기 신호 전달 성능이 떨어지기 마련이다. 또 솔더볼 자체 크기 때문에 입출력(I/O) 수를 확대하는데 한계가 있다. 즉 솔더볼 간격을 좁힐 수 없어 상하의 신호 전달 통로를 많이 만들 수 없다는 뜻이다.

현재 시스템 반도체의 솔더볼 간격은 21~24마이크로미터(㎛) 수준으로 알려졌다. 간격이 넓어 입출력 수를 가늠하는 척도인 집적도(범프/㎟)가 2000 안팎에 불과하다.

솔더볼을 사용하지 않고 구리와 구리를 직접 연결하는 하이브리드 본딩은 범프 간격(입출력 단자의 간격)이 4㎛급이다. 입출력 집적도도 6만2500에 달한다. 수많은 입출력 단자를 확보해 빠른 신호 전달이 가능하다는 뜻이다. 삼성전자가 2026년 하반기에 개발할 하이브리드 본딩 기반 AP는 범프 간격이 2㎛ 이하로 입출력 집적도는 25만에 달할 것으로 전망된다.

◇HBM도 하이브리드 본딩으로 전환

메모리 영역에서도 기존 열압착 본딩에서 하이브리드 본딩 전환이 이뤄지고 있다. 바로 HBM이다. 삼성전자는 HBM4(6세대)에 하이브리드 본딩과 기존 열압착 본딩을 동시에 적용, 개발을 진행하고 있다. 하이브리드 본딩 성과를 파악, 이후 세대에는 본격적인 대전환이 이뤄질 것으로 전망된다. 현재는 HBM3(4세대)를 기반으로 16단 높이까지 하이브리드 본딩으로 구현, 안정적으로 기능이 작동하는 단계까지 왔다.

HBM에서 하이브리드 본딩을 적용하면 위·아래 D램 간 접합 간격이 줄어든다. 기존에는 솔더볼이 있었지만, 하이브리드 본딩은 상하 구리가 맞닿기 때문에 사실상 간격이 없다. 현재 열압착 방식은 D램 간격이 약 7㎛ 수준이다. 매우 좁지만 이 마저도 D램 간 거리를 만들어 신호 전달을 제한하고, HBM 패키지 전체가 높아진다. 하이브리드 본딩은 같은 단수로 쌓을 경우 열압착보다 높이가 낮다.

삼성전자가 자체적으로 분석 결과, 같은 D램 칩일 경우 하이브리드 본딩이 33% 더 공간(높이)을 확보할 수 있는 것으로 파악됐다. 열 저항 효율은 20% 개선되는 것으로 나타났다. 삼성전자는 하이브리드 본딩이 적용된 HBM4를 2025년 양산 목표로 개발 중이다.

◇TC-NCF VS MR-MUF 논쟁 사라질까

삼성전자는 현재 HBM에 비전도성필름(NCF)를 적용하고 있다. D램을 상하로 붙이기 위해서다. 솔더볼을 고정하고 HBM을 접합하는 이 소재는 업계에서 많은 논쟁을 낳았다. 성능 때문이다. 삼성전자는 NCF를, 경쟁사인 SK하이닉스는 액체성 몰디드언더필(MUF) 소재를 HBM 접합에 쓰는데, 어떤 소재가 더 뛰어난가에 대한 이슈가 끊임없이 제기되고 있다. 접합 소재는 D램 접합 뿐 아니라 열 방출 등 HBM 성능을 좌우하기 때문이다.

하이브리드 본딩에서는 위·아래 반도체가 맞붙기 때문에 접합 소재가 필요없다. 이 때문에 NCF와 MUF 소재 활용 수요도 줄어들 것으로 전망된다. 패키징 업계 관계자는 “양사가 모두 HBM에 하이브리드 본딩을 적용할 2026년에는 접합 소재 경쟁이 한풀 꺾어 들 수 있다”며 “시스템 반도체에서도 같은 상황이 펼쳐질 것”이라고 내다봤다.

소재 성능 대신 공정 기술력이 하이브리드 본딩 시대에는 경쟁 우위를 가를 핵심 역량으로 손꼽힌다. 특히 업계에서는 웨이퍼 연마와 절단(쏘잉) 기술에 주목하고 있다. 상하 반도체를 전기적으로 연결하기 위한 구리를 최대한 잘붙게 연마하는 기술이 대표적이다. 웨이퍼에서 TSV 공정 후 구리를 주입했을 때 끝 단을 효율적으로 깔끔하게 연마해야 한다. 이 때문에 웨이퍼 연마 방식 중 하나인 화학적기계연마(CMP) 기술력이 하이브리드 본딩 성과를 좌우할 것으로 전망된다.

패키징 업계 고위 관계자는 “또 하이브리드 본딩에서 이물을 최소화하는 방식으로 웨이퍼를 절단하는 것도 중요하다”며 “이를 위한 정밀한 계측 기술도 필요하다”고 밝혔다.

'Guide Ear&Bird's Eye6 > 산업의 쌀 반도체(5G. 인공지능, 자율주행. 태양광 재생에너지 등 )' 카테고리의 다른 글

| 데이터 주도 시대 AI 및 차세대 오토모티브 최적화 칩 ‘eMRAM’의 기초 이론 (0) | 2024.06.03 |

|---|---|

| [인터뷰] 초거대 AI 시대의 랜드마크, 삼성전자 V낸드 (0) | 2024.05.26 |

| LPDDR (0) | 2024.05.24 |

| HBM엔 침묵한 젠슨 황, "LPDDR이 서버 전력 소모 줄여" (0) | 2024.05.23 |

| 삼성, 2나노 AP '테티스' 프로젝트 착수...2026년 '갤럭시 S26' 탑재 예상 (0) | 2024.05.23 |